Embedded Projects Overview

This section will cover a wide range of embedded projects I have worked on during my academic career, ranging from BLE communication to Computer VIsion.

Telegraph: Intelligent Combat Systems

Telegraph is a fully integrated, real-time boxing analytics platform designed to elevate athletic performance through intelligent data capture and machine learning. I served as the Hardware and Product Development Lead, co-developing the physical system architecture and overseeing integration with our mobile analytics pipeline.

We engineered a low-profile embedded device using an ESP32-S3 and IMU, housed in a 3D-printed enclosure that fits inside a boxing glove. Telegraph detects, classifies, and evaluates boxing strikes in real time, transmitting data over BLE to a mobile app that displays force, explosiveness, velocity, and fatigue metrics. Our system achieved over 98% classification accuracy, <500ms latency, and over 3 hours of battery life on a single charge.

Built for high-level athletes and coaches, Telegraph helps users refine technique, track progress, and gain actionable insights during and after training sessions. Its sleek design and robust software pipeline offer a compelling alternative to bulkier or less insightful systems on the market. On demo day, our team ended up placing 3rd overall in the popular vote, speaking to the robustness and innovation of Telegraph.

Read more

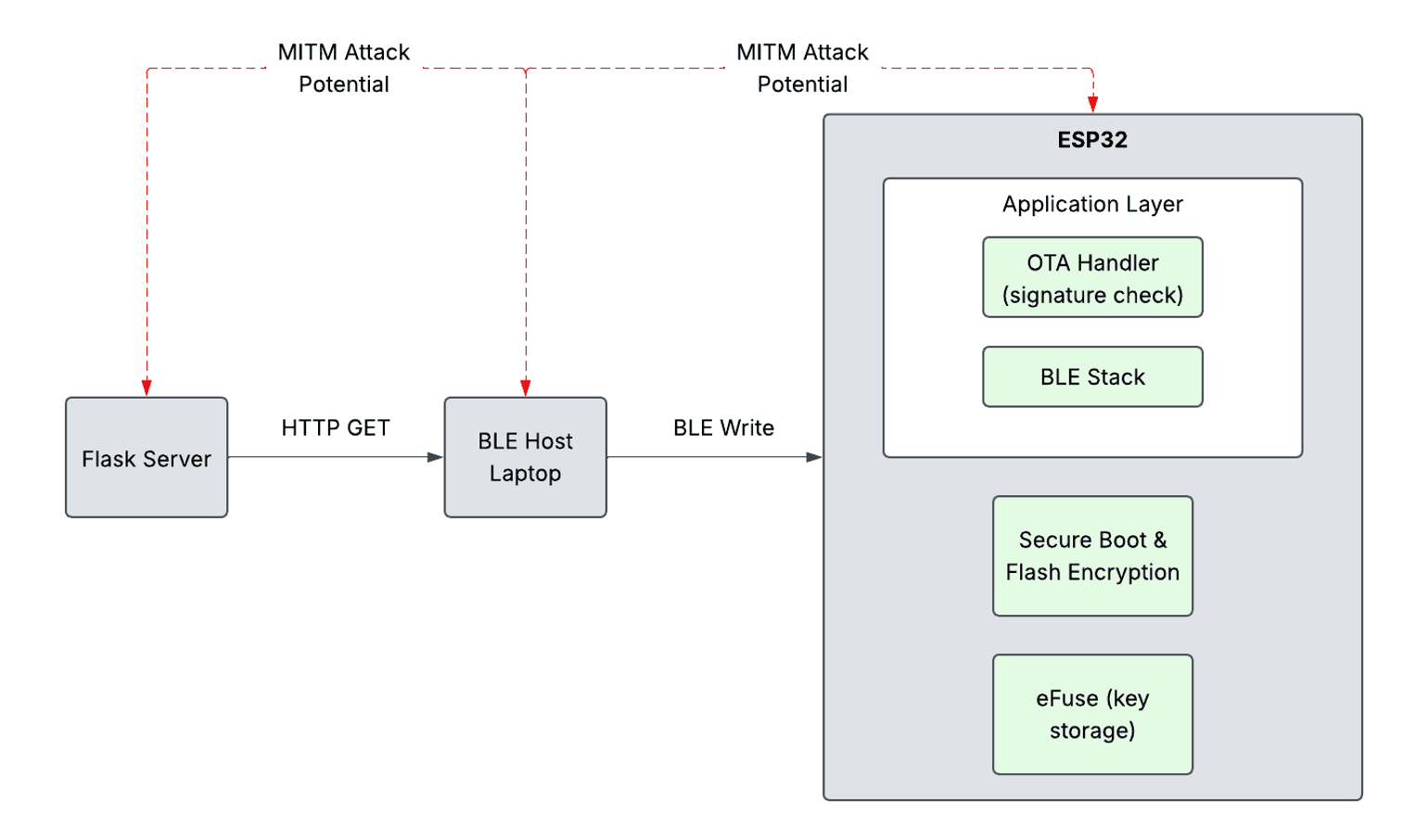

Secure OTA over BLE Firmware Transfer

To address the growing need for secure firmware updates in IoT ecosystems, our team engineered a secure Over-the-Air (OTA) update framework for the ESP32-S3 microcontroller, focusing on cryptographic validation, BLE transmission, and rollback protection. I led the development of the core OTA logic using the ESP-IDF, implementing firmware upload, validation, and partition management.

We utilized SEMECS digital signatures to ensure firmware authenticity and integrated the ESP32’s eFuse module for secure public key storage. Firmware was transmitted over a custom BLE GATT service, then verified and applied using a segmented update protocol. Our system featured real-time UART logging, rollback fallback, and performance-optimized verification, achieving OTA reliability with minimal resource overhead.

Performance testing showed our OTA pipeline could handle secure firmware transfers up to 540KB in under 6 minutes with <3ms signature verification time. While not encrypted end-to-end, the system was robust against signature spoofing and partial image injection. Further improvements were proposed for chunk-level hashing and dashboard-based update management.

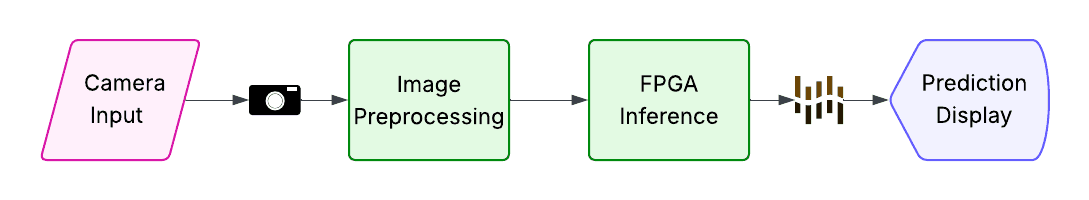

Handwritten Digit Recognition with FPGA Inference

This project focused on building a complete embedded digit recognition pipeline using the DE1-SoC FPGA board. After training a neural network on the MNIST dataset, we performed hardware-accelerated inference on grayscale 28x28 images captured using the onboard D5M camera.

We adapted and extended existing OpenCL kernels from previous labs to implement a tiled, weight-stationary inference engine on the FPGA fabric. I wrote and debugged performance-critical sections in C++ (main.cpp), interfacing with the trained weights and managing OpenCL kernel memory. After deploying our .aocx FPGA configuration and reprogramming the board, we achieved successful digit classification for real-world inputs via the ARM host processor and FPGA coprocessor.

In addition to FPGA programming and weight deployment, we implemented image preprocessing in C using a custom image scaler to convert 240x240 grayscale input from the camera to 28x28, compatible with the MNIST-trained model.

Github Repo

© Luke Malkasian - 2025